Blog

Boot up! Understanding RISC-V Runtime Initialization

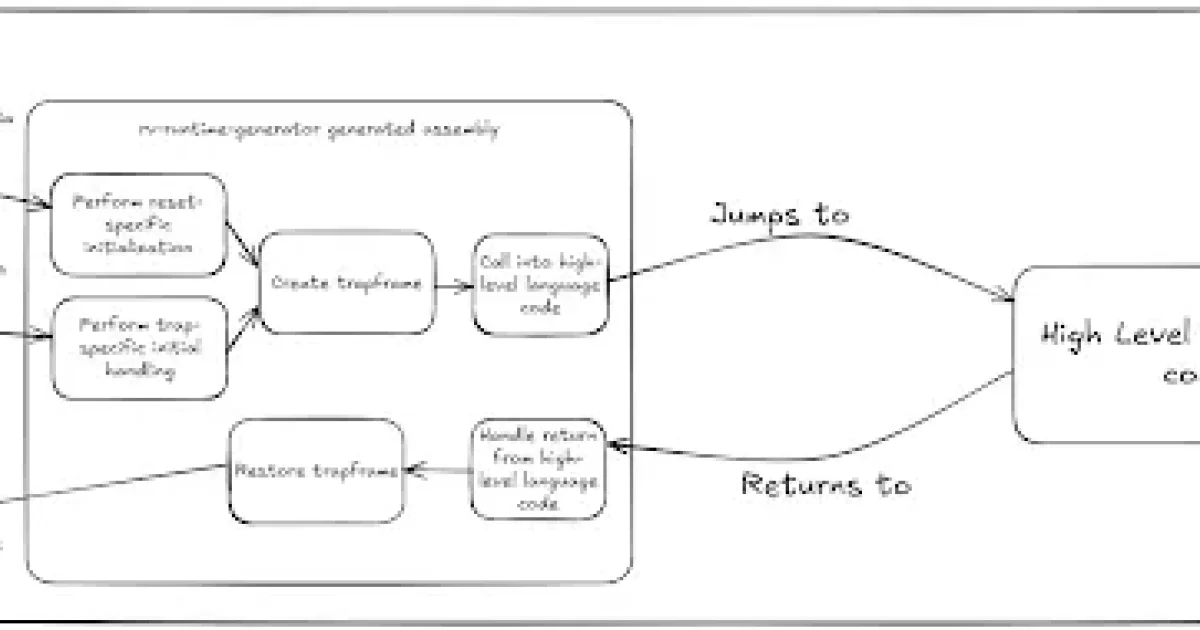

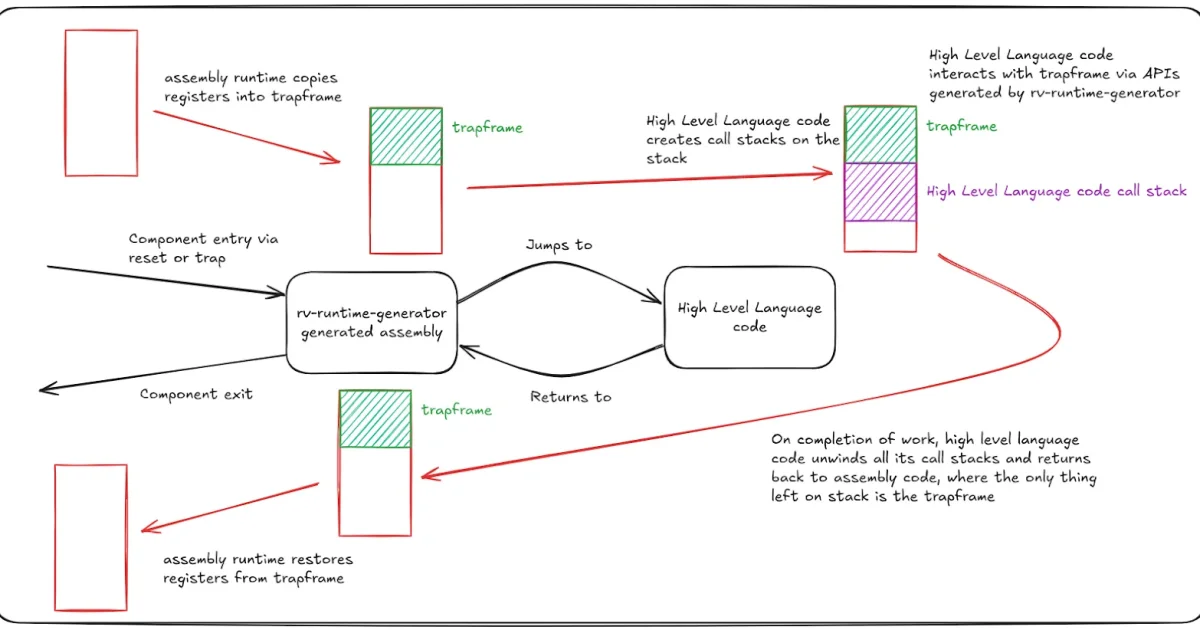

In our previous post [1], we explored the architecture of rv-runtime-generator [3] and introduced its first key data structure — the trapframe. Now, we’ll shift our focus to the boot up path…

Diving into the architecture of rv-runtime-generator

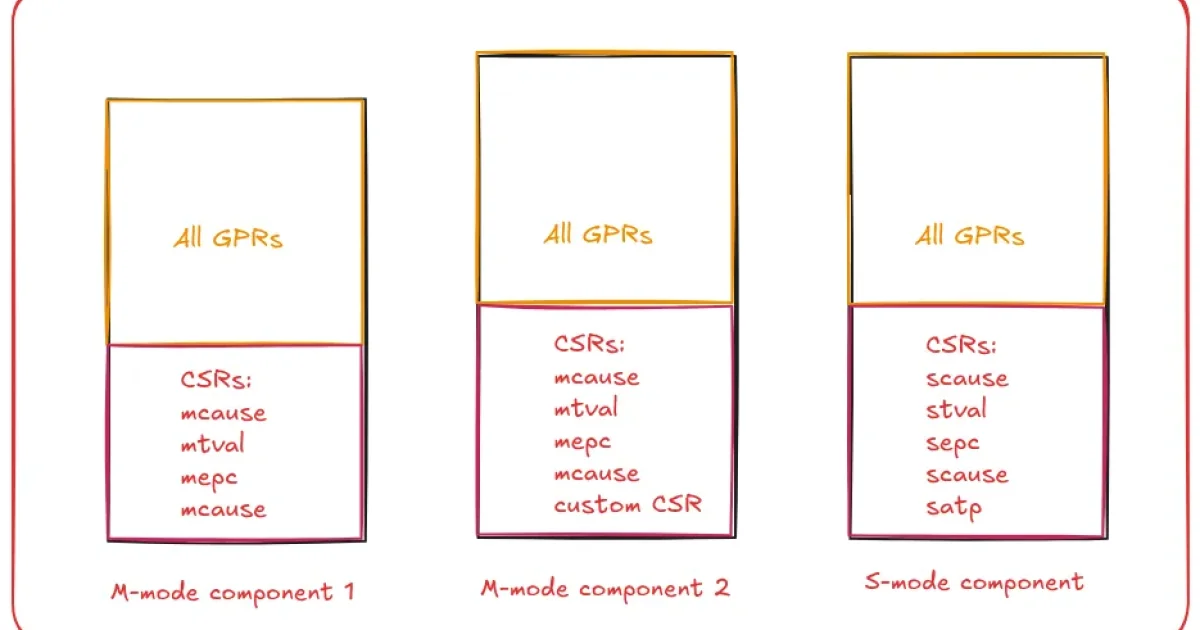

In the previous post[3], we explored the background, motivation and requirements for the rv-runtime-generator[4] tool. This post delves into the detailed design and architecture that powers this essential component of RISC-V…

Bootstrapping RISC-V Systems: Introducing rv-runtime-generator

Background System software development presents a fundamental challenge that every bare metal project must solve: bridging the gap between the processor’s minimal boot state and a fully functional execution environment…

Easy Installation of Binary Python Packages on riscv64 Devices

Why can it be difficult to install Python packages on riscv64 devices? The Python Package Index (PyPI) offers both pure Python and binary packages. Binary packages, which are pre-compiled, require…

Advancing Go on RISC-V: Progress Through the RISE Project

Since early 2024, the Go programming language has seen significant progress on the RISC-V architecture, largely due to ongoing efforts within the RISE Project and key contributions to the Go…

RVA23 Profile: Unlocking new possibilities for RISC-V in high-performance, compute-intensive workloads

Following the recent RISC-V North America Summit I sat down with Ved Shanbhogue, to discuss the announced RVA23 profile and its potential impact on the RISC-V Server space. Ved Shanbhogue…

Announcing the RISE RISC-V Developer Appreciation Pilot Program: Empowering Developers to Expand RISC-V’s Reach

At RISE, we’re always looking for ways to strengthen the RISC-V architecture and expand its adoption across the software ecosystem. To take this vision further, we’re excited to announce the…

RISE Discusses RISC-V Software Acceleration at RISC-V Taipei Day 2024

We just concluded a highly successful RISC-V Taipei Day, where the enthusiasm and engagement of the RISC-V community were evident. Attendees gathered in large numbers to explore the latest advancements and…

Help us contribute to the RISC-V Optimization Guide

In the world of computing, performance is key. As RISC-V continues to rise in popularity for its open standard instruction set architecture, achieving the highest performance from RISC-V chips is…

Leveraging Scaleway to support the RISC-V Software Ecosystem

At RISE, we have leveraged Scaleway’s RISC-V EM-RV1 offering to support major open-source projects like Adoptium, Go, AlmaLinux, and RockyLinux. Scaleway provides bare-metal RISC-V instances tailored to the needs of open-source projects,…

Java on RISC-V: RISE and Eclipse Adoptium Partnership

In an exciting development, RISE has partnered with the Eclipse Adoptium Working Group to bring Java to the RISC-V architecture. This collaboration ensures that Java developers can now leverage the…