Resources

Blog

Rivos Collaborates to Complete Secure Provisioning of Integrated OpenTitan Root of Trust During SoC Production

Rivos is pleased to announce the successful secure provisioning of the integrated OpenTitan open source Root of Trust (RoT) in its SoC. This was done during the chip production process…

Blog

Unlocking Next-Generation AI: The Critical Role of Compute, Memory, and Interconnect

Last week, I joined a panel discussion exploring a topic that’s shaping the future of AI: the need to refocus on the interplay between compute, memory, and interconnect technologies. Too…

Blog

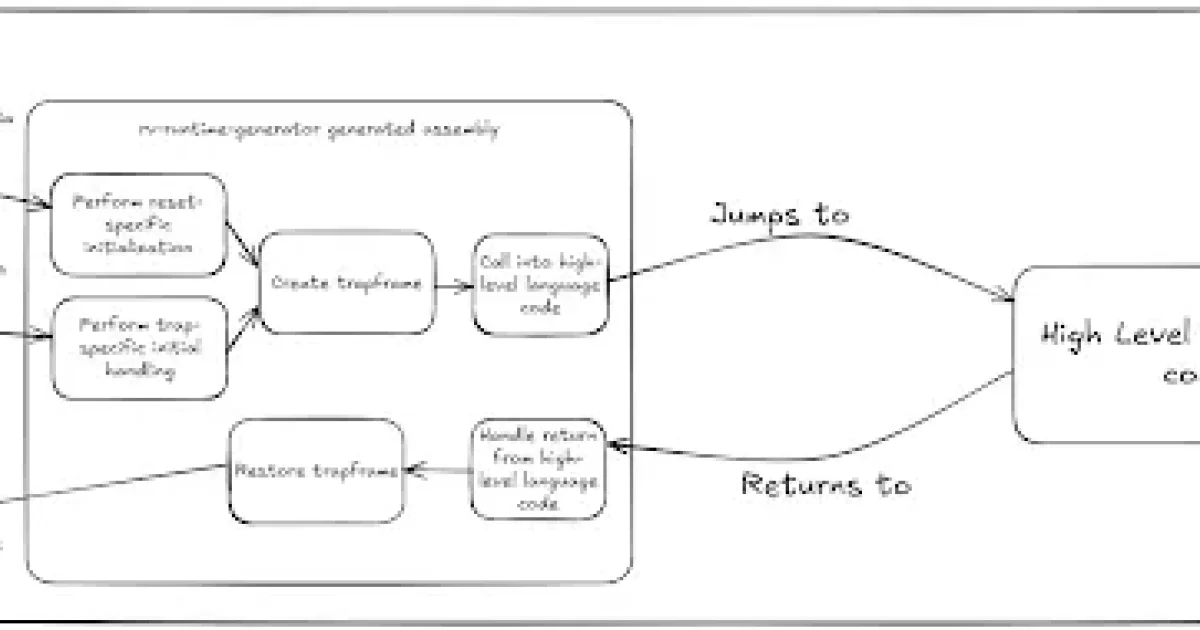

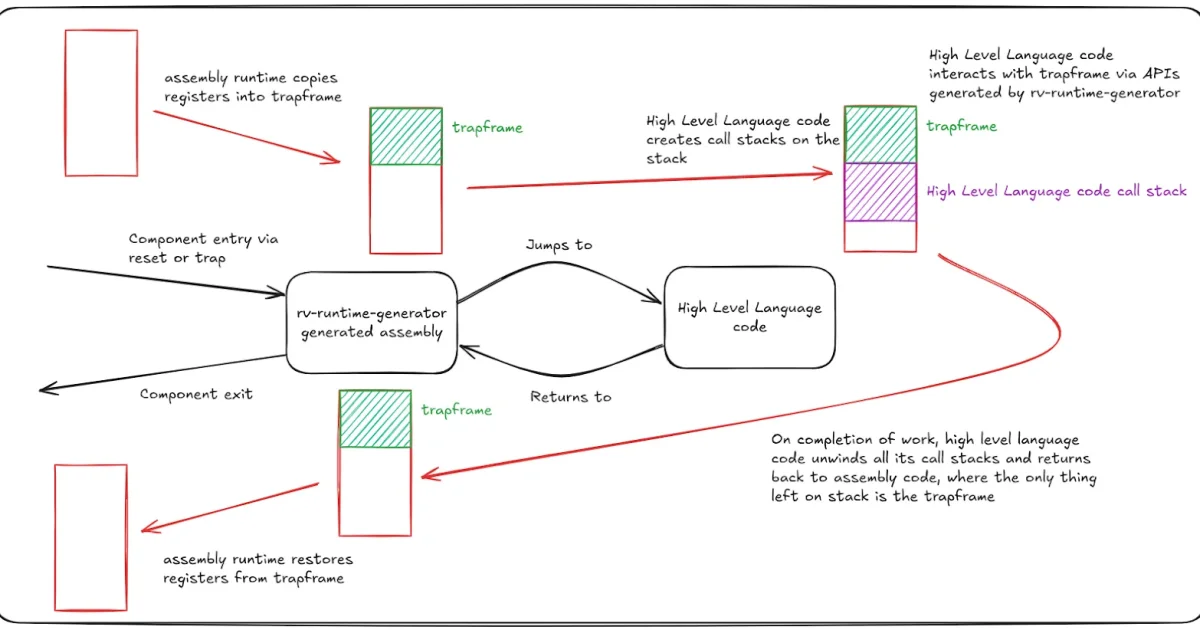

Boot up! Understanding RISC-V Runtime Initialization

In our previous post [1], we explored the architecture of rv-runtime-generator [3] and introduced its first key data structure — the trapframe. Now, we’ll shift our focus to the boot up path…

Blog

Ultra Ethernet Specification 1.0 – A Game Changer for AI Networking

The Ultra Ethernet Consortium (UEC) has dropped its new Ultra Ethernet Specification 1.0, and it’s a game-changer for AI networking, especially for the ‘backside’ networks that interconnect GPUs. (This post…

Blog

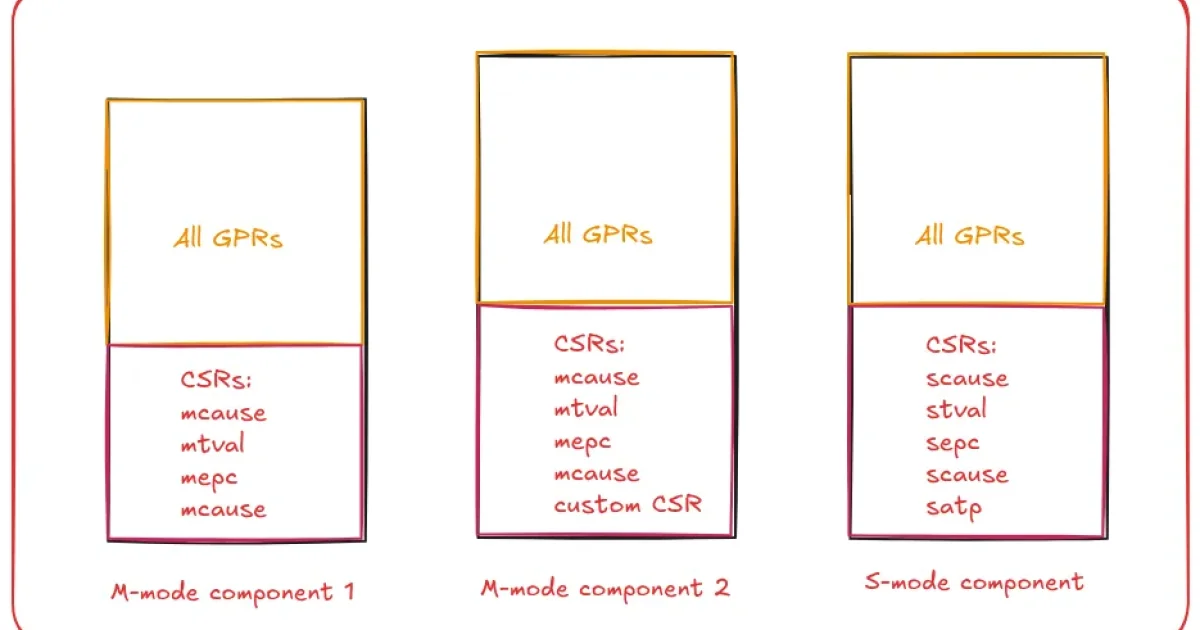

Diving into the architecture of rv-runtime-generator

In the previous post[3], we explored the background, motivation and requirements for the rv-runtime-generator[4] tool. This post delves into the detailed design and architecture that powers this essential component of RISC-V…

Blog

Bootstrapping RISC-V Systems: Introducing rv-runtime-generator

Background System software development presents a fundamental challenge that every bare metal project must solve: bridging the gap between the processor’s minimal boot state and a fully functional execution environment…

Announcement

Rivos Accelerates Chip Verification with Spillbox’s Hybrid Cloud Bursting Solution

As chip architectures become more complex, the demands of simulation workloads grow beyond them. Rivos™ Inc., a leader in high-performance and power-efficient server solutions built on RISC-V, has successfully adopted…

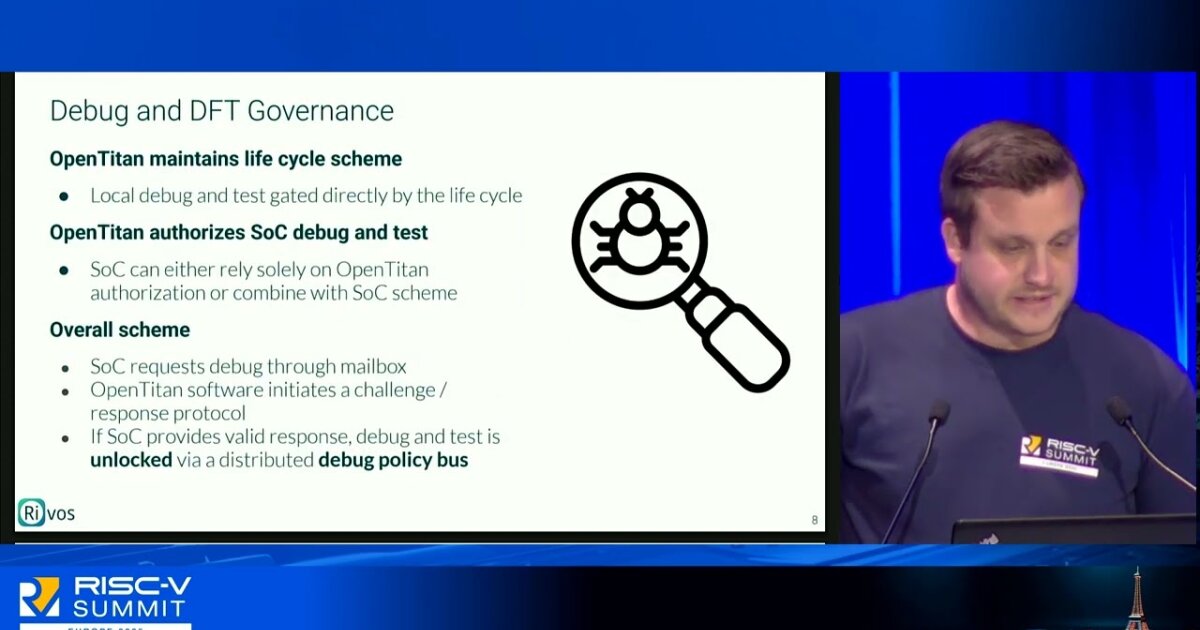

Talk

OpenTitan Integrated: A RISC-V Open-Source Silicon Root-of-Trust for large SoCs

Modern System-on-Chips (SoCs) rely on a secure Root of Trust (RoT) as the foundation for all security services. Compromise of the RoT can have catastrophic consequences, undermining the security of…

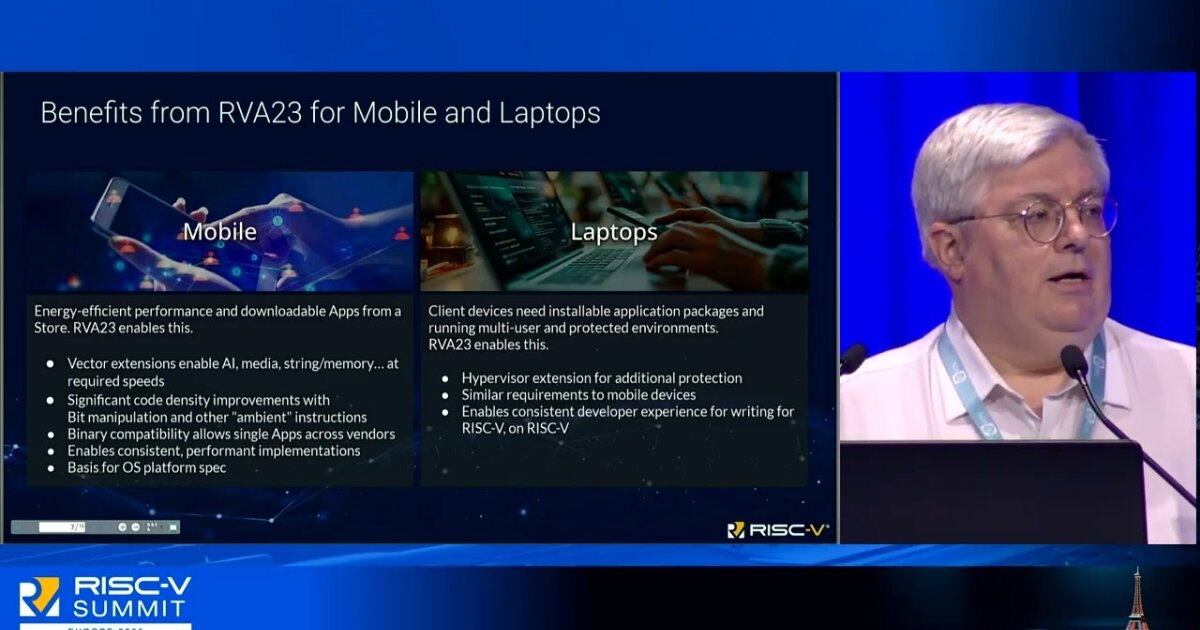

Talk

The Significance of the RVA23 Profile in Advancing RISC-V Ecosystem ( RISC-V Summit Europe)

The RVA23 profile represents a key development in the RISC-V architecture, standardizing the 64-bit application processors ISA for seamless software portability across hardware implementations. This simplifies development and supports RISC-V…

Talk

The RISE Project: Advancing RISC-V Software ( RISC-V Summit Europe)

The RISC-V Software Ecosystem (RISE) Project is in high gear investing time and money on software to support RISC-V, including more than $500K on contracts for further enhancements. This talk…

Blog

Easy Installation of Binary Python Packages on riscv64 Devices

Why can it be difficult to install Python packages on riscv64 devices? The Python Package Index (PyPI) offers both pure Python and binary packages. Binary packages, which are pre-compiled, require…

Blog

Advancing Go on RISC-V: Progress Through the RISE Project

Since early 2024, the Go programming language has seen significant progress on the RISC-V architecture, largely due to ongoing efforts within the RISE Project and key contributions to the Go…